DGIST 전기전자컴퓨터공학과 박사과정 위정윤

#### **Session 5 Incremental ADCs**

2025 IEEE CICC의 Session 5에서는 "Incremental ADC"를 주제로 총 3편의 기술 논문이 발표되었다. Incremental ADC는 높은 에너지 효율을 제공하는 구조로, multi-step 양자화를통해 정밀도를 향상시키거나, 단일 스텝 구조에서도 기존의 free-running 방식보다 우수한 성능을 달성하려는 다양한 연구가 진행되고 있다. Multi-step 양자화 방식에서는 첫번째와 두 번째 단을 연결하는 residue amplifier의 이득 정확도를 높이거나, 전체 구조의에너지 효율을 극대화하는 방향으로 연구가 집중되고 있다. 반면, 단일 스텝 기반의 구조에서는 루프 필터의 차수 및 OSR(oversampling ratio)을 조정하여 최적의 noise shaping특성을 구현하고, 선형성 저하의 주요 원인이 되는 DAC 설계에 초점을 맞춘 연구가 활발히 이루어지고 있다.

# #5-2 A 133.6-μW 1kHz-BW Multi-bit 2nd-order Incremental ADC Achieving 115.4-dB SNDR with Low-Cost Coarse-Sorting DEM and Zip-Extended-Counting

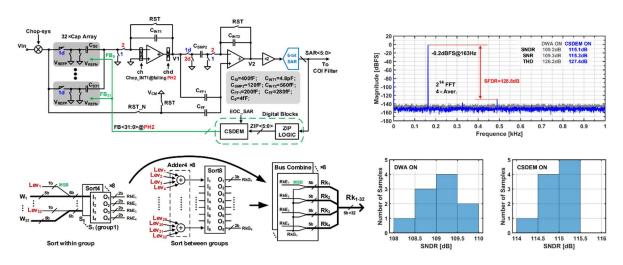

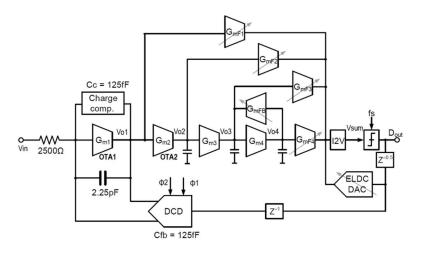

본 논문에서는 1kHz 대역폭을 갖는 2차 Incremental ADC 구조를 제안하였다. DAC mismatch로 인한 비선형성을 효과적으로 평균화하기 위해 Coarse-Sorting DEM 기법을 도입하였으며, 이를 통해 115.4dB의 높은 SNDR을 달성하였다. 또한, Zip-Extended-Counting 기법과 6bit SAR quantizer를 결합하여 단일 스텝 Incremental ADC에서 extended counting 동작을 구현하였으며, 이는 5bit SAR quantizer, 이득 2의 residue amplifier, 그리고 1회의 extended counting을 조합한 것과 동등한 성능을 제공한다. Incremental ADC는 매 변환마다 적분기가 초기화되기 때문에, free-running ADC와 달리 DEM을 통한 mismatch 평균화 효과가 제한적이다. 특히 루프 필터의 차수가 높고 OSR 이 낮을 경우, 각 샘플의 timing에 따라 mismatch가 출력에 다르게 반영되어 선형성 저하가 더욱 두드러지는 문제가 발생한다. 이를 해결하기 위해 본 논문에서는 저복잡도 구조의 Coarse-Sorting DEM (CSDEM)을 제안하였다. 제안된 기법은 5bit DAC, 즉 32개의 unit element에 대해, 인접한 4개의 element 내부에서 rank를 구하고, 이를 다시 4개씩 그룹화하여 그룹 간 rank를 계산한 뒤, 최종적으로 결합된 rank에 따라 weight를 설정하는 방식으로 동작한다. 이때 각 element는 level register와 weight register를 통해 상태가 추적되며, 해당 정보를 기반으로 partial sorting을 수행한다. 제안된 CSDEM은 기존

[그림 1] 제안된 시스템과 Coarse-Sorting DEM 기술 및 효과

Smart-DEM과 비교할 때 구조적으로 큰 차별성을 가진다. Smart-DEM은 mismatch 평균화 성능이 우수하나, 완전한 정렬(sort)과 고속 클럭(N²×Fs)에 의존하여 하드웨어 복잡도와 전력 소모가 급격히 증가하는 단점이 있다. 반면 본 논문에서 제시한 CSDEM은 partial sorter와 coarse-sorting 알고리즘을 활용하여 이러한 복잡도를 O(N) 수준으로 억제하였으며, 496개의 10-bit comparator가 필요한 기존 구조 대신 48개의 7-bit comparator만으로 충분한 mismatch suppression 효과를 제공함을 보였다. 다만, 제안된기술의 효과를 더욱 명확히 입증하기 위해서는 일반적인 정현파 입력뿐 아니라 다양한입력 시나리오에 대한 PSD(전력 스펙트럼 밀도) 분석 결과가 함께 제시된다면, CSDEM기법의 전반적인 안정성과 범용성을 더욱 설득력 있게 강조할 수 있을 것으로 기대된다.

# #5-3 A 16-bit Incremental ADC Enabled by An Efficient Shooting Integrator with Inherent Noise Reduction

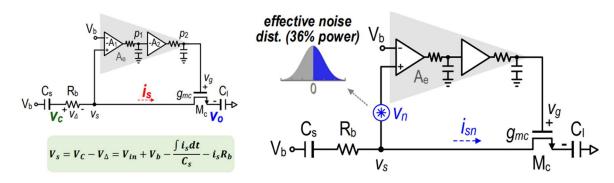

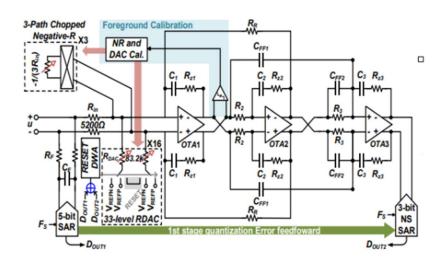

본 논문에서는 새로운 "shooting integrator" 구조를 기반으로 한 2차 incremental  $\Delta\Sigma$  ADC (I $\Delta\Sigma$ M)를 제안한다. 기존의 switched-capacitor 기반 integrator는 적분기의 settling 시간, 커패시턴스 크기, 출력 선형성 등 다양한 아날로그 설계 요소에 의해 전력 소모와 성능 간 trade-off가 발생하며, 증폭기 설계의 복잡도 또한 상당히 높은 편이다. 이러한 한계를 극복하기 위해 본 논문에서는 feedback loop와 barrier resistor를 이용해 반복적인 전하 전달(shooting transfer)을 수행하는 shooting integrator를 제안하였다. Shooting integrator는 입력 커패시터( $C_s$ ), barrier resistor(Rb), 그리고 error feedback amplifier(Ae)로 구성되며, 전하가 고속으로  $C_s$ 에서 적분 커패시터  $C_t$ 로 이동하는 과정을 반복함으로써 안정적이고 선형적인 전하 전달을 구현한다. 이 과정에서 comparator나 ring amplifier처럼 과도 응답이나 overshoot를 유발할 수 있는 구조적 불안정성이 제거되어 매우 정밀한 적분 동작이 가능하다. 특히 Ae는 오직 증폭기의 DC 이득과 극점 위치만을 고려해 설계하면 되며, 정착 속도나 커패시턴스의 크기에 크게 영향을 받지 않기 때문에 증폭기

[그림 2] 제안된 shooting 적분기

의 복잡도와 전력 소모를 대폭 줄일 수 있다. 기존의 integrator 설계에서는 선형성, 출력 스윙, 출력 공통 모드 레벨 등의 요소가 매우 민감하게 작용하여 회로 성능을 제한하였으나, shooting integrator 구조에서는 이러한 항목들이 더 이상 주요 제약 요소로 작용하지 않는다. 실제로 제안된 16-bit incremental ADC는 shooting integrator를 핵심으로 채택하여 180nm CMOS 공정에서 제작되었으며, 500kHz 클록 기준으로 6.28µW의 낮은 전력을 소모하면서도 최고 97.5dB의 SNR과 174dB의 Schreier FoM을 달성하였다. 또한 pseudo-differential 구조와 결합될 경우 shooting 과정에서 발생하는 노이즈가 Gumbel 분포를 따르며, 경로 간 최대 노이즈가 상쇄되어 최대 75%까지 노이즈 파워를 억제할수 있음이 확인되었다. 결과적으로, 본 논문에서 제안된 shooting integrator는 기존 SC integrator의 복잡한 설계 제약을 제거하고, 전력 효율을 극대화하면서도 고정밀의 성능을 달성할 수 있는 새로운 적분기 구조로서 우수성을 입증하였다. 향후 이 구조는 고정밀 저전력 데이터 컨버전 시스템의 핵심 요소로 널리 활용될 수 있을 것으로 기대된다.

# #5-4 A 50-kHz BW 92.1-dB SNDR Incremental ADC Using a Back-End Sampling Two-Step NS-SAR Architecture with Concurrent Gain-Error + Noise Suppression

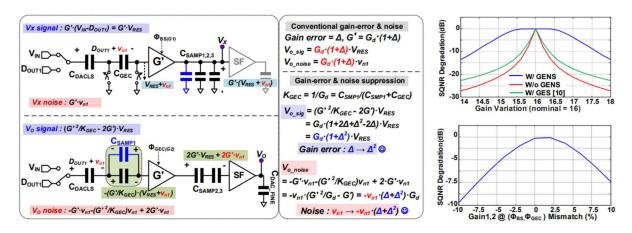

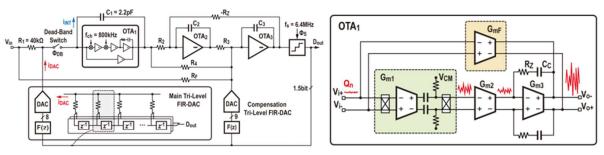

본 논문에서는 50kHz 대역폭을 갖는 Noise-Shaping SAR ADC(NS-SAR ADC) 기반의 two-step Incremental ADC 구조를 제안한다. 첫 번째 단계에서는 continuous-time tracking SAR ADC를 활용하여 AC-coupled 입력 신호를 양자화하고, 그 결과는 CDAC 에 샘플링된다. 이후 CDAC 을 입력 노드에 연결하면, 출력에는 첫 번째 단계에서 제거되지 않은 잔류 전압만이 남는다. 이 잔류 전압은 Concurrent Gain-Error and Noise Suppression(CGENS) 기법을 통해 이득 오차를 억제하며 증폭되고, 두 번째 단계에서 NS-SAR ADC 에 의해 정밀하게 양자화된다. Two-step 구조에서 첫 번째와 두 번째 단을 연결하는 residue amplifier의 이득 정확도는 최종 SQNR 성능을 결정하는 핵심 요소이다. 일반적으로 에너지 효율 향상을 위해 floating-inverter 기반 증폭기가 널리 사용되나, 고정된 이득 특성으로 인해 gain error 가 발생하며 이는 SQNR 및 선형성 저하로 이어지는 문제가 있다. 본 논문에서는 이러한 한계를 극복하기 위해, floating amplifier 의

[그림 3] 제안된 이득 에러 효과 억제 기술

gain error 를 효과적으로 억제하는 기법을 제안함으로써, 높은 선형성과 SQNR을 동시에 달성하였다. 제안된 기법은 전력 효율을 유지하면서도 선형성을 개선할 수 있다는 점에서 중요한 장점을 갖는다.

# 저자정보

위정윤 박사과정 대학원생

한국과학기술원 바이오및뇌공학과 박사과정 석동열

## Session 13 High-Speed Nyquist ADC

이번 2025 IEEE CICC의 Session 13, High-Speed Nyquist ADC에서는 총 5편의 논문이 선정되어 발표되었다. 이 세션에서는 Nyquist 샘플링을 수행하는 고속 ADC의 성능 개선을 주제로 하는 연구를 다루고 있으며, time-interleaved ADC에서의 시간 오차(timing-error)로 인한 노이즈를 극복하기 위해, TD(time-domain), SAR(successive approximation register), pipelined 등 다양한 ADC 기본 구조를 융합 하여 속도 및 해상도 개선을 이루어 낸 사례, 고속 ADC에서 PVT 변화 대응을 위한 연구 등이 소개되고 있다.

#13-1 본 논문은 중국 전자과기대학(UESTC) 연구진 등이 게재한 논문으로 10b 해상도로 13GS/s 수준 고속 샘플링 성능을 보여주는 주파수-인터리빙(frequency-interleaved) 방식의 ADC 연구를 소개하고 있다. 고속 샘플링에서 자주 활용되는 기법인 시간-인터리빙(time-interleaved)은 병렬로 구성된 ADC가 아주 짧은 시간차를 두고 교대로 샘플링하는 방식으로 고속 샘플링을 구현해 낼 수 있지만, ADC 간 샘플링 시간(timing) 오차가 바로고주파 영역에서의 성능(SNDR 등) 저하로 이어지는 문제가 있다.

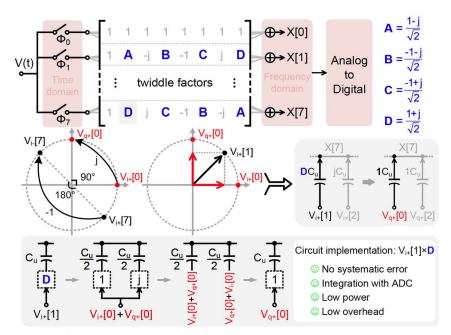

연구진은 이를 극복하기 위하여 시간-인터리빙 방식으로 시스템에 유입되는 radix-8의 아날로그 푸리에 연산을 통해 주파수 도메인의 값으로 변환하여 출력하는 방식으로 시간 오차에 대한 ADC의 민감성을 떨어뜨렸다. 또한, 푸리에 변환 연산을 위한 복소수 계수 값을 스위치-커패시터를 활용한 전하 재분배(charge redistribution) 방식을 이용하여 생성하여 대역통과필터를 활용한 기존의 주파수 분할 방식에 비해 전력 효율면에서도 이점을 보여주었다. 그 결과 jitter, bandwidth mismatch, time skew 등 시간 오차가 유발되었을 때, 시간-인터리빙 방식의 샘플링에 비해 나은 성능을 SNDR 등의 지표에서 13GS/s 수준의속도에서 나은 SNDR 지표를 보여주었다. 측정 결과로 SNDR 45.8[dB], SFDR 56.1 수준의성능을 보고했으며, 26.4mW 수준의 전력소모, 12.7 fj/conv.-step 수준의 Walden FoM을 달성하여 기존 연구와의 차별성을 보여주었다. 본 회로는 28nm CMOS 공정으로 제작되었으며 활용한 면적은 0.126mm² 이다.

Fig. 2. Circuit implementation of the radix-8 AFT with irrational coefficients.

[그림 1] Xingchen Chao와 연구팀은 커패시터 충·방전 제어로 실시간 radix-8 푸리에 변환 위한 복소수 계수(complex coefficients)를 구현하였으며, 이를 활용한 주파수-인터리빙 ADC(frequency-interleaved ADC)를 선보였다. 주파수-인터리빙 ADC는 시간오차에 상대적으로 둔감하여 비슷한 조건의 고속 샘플링에서 시간-인터리빙 ADC에 비해 시간오차에 견고하며, 더 나은 A/D 변환 성능을 보여준다.

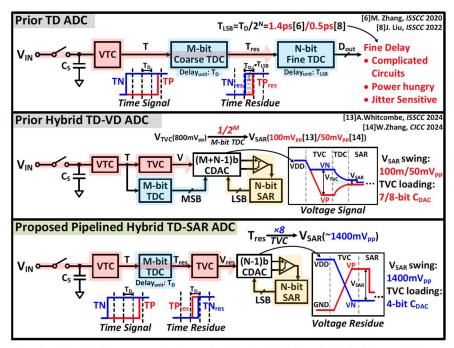

#13-2 본 논문은 마카오 대학을 포함한 총 6개 연구기관의 연구팀이 참여한 연구를 소개하고 있다. 전력효율성이 높은 고속 ADC 설계를 위해 고속 샘플링이 가능한 TD-ADC(time-domain ADC, 시간 도메인 ADC)와 SAR(successive approximation register) ADC를 결합한 하이브리드 TD-SAR ADC를 제안했다. TD-ADC의 경우 고해상도를 얻기위해서 많은 딜레이 셀이 필요하며, 이를 확보하기 위해서 면적, 전력과 같은 자원이 많이 필요하다는 단점이 있으며, PVT 변화에 성능이 민감하게 달라진다는 한계를 가지고있으며, SAR의 경우 전력 효율이 뛰어나고 구조가 단순한 반면 A/D 변환을 위해 여러차례 비교가 필요한 특성을 인해 고속 샘플링에서는 한계에 마주하게 된다.

연구진은 이러한 한계를 극복하고 양 구조의 이점을 충분히 활용하기 위하여 입력단에서는 TD-ADC 구조를 활용하여 고속으로 MSB를 결정하고 나머지 값(residue)에 대해서는 시간-전압 변환 회로(TVC, time-voltage converter)를 활용하여 전압 값으로 변환한 뒤 5-bit SAR를 이용하여 나머지 값을 양자화하는 과정을 거치는 파이프라인을 구성하였다. 제안하는 구조에서는 TD-ADC에서 3bit를 결정하고, 나머지 값을 5-bit SAR(샘플링 속도: 3.125GS/s)로 결정하여 총 7bit의 해상도를 갖는 구조이다. 이러한 방식으로 12.5GS/s 수준의 고속 샘플링을 하면서도 전력 효율을 끌어올려 14.7mW 수준의 전력 소모,

24.3fJ/conv-step의 Waldon FoM을 달성하였다. 또한, 12.5 GS/s의 고속 샘플링에서 35.45[dB] 수준의 SNDR, 48.28[dB] 수준의 SFDR을 달성하였으며, 0.5에서 6.5GHz의 입력 주파수 구간에서 2.7dB 이내의 SNDR 변화, -20℃에서 80℃ 사이의 온도변화에서도 2dB 이내의 SNDR 변화를 보고하였다. 본 회로는 28nm CMOS 공정으로 제작되었으며, 총 0.0126 mm²의 면적 안에 제작되었다.

Fig. 1. Block diagram of the prior TD ADC (top), hybrid TD-VD ADC (middle) and the proposed pipelined hybrid TD-SAR ADC (bottom).

[그림 2] Haoyu Li와 연구팀은 고속 샘플링이 가능한 TD-ADC의 이점과 에너지 효율성이 높은 SAR-ADC의 이점을 모두 활용할 수 있는 하이브리드 형의 파이프라인 하이브리드 TD-ADC를 제안하였다. (그림 2의 가장 아랫상자)

#### 저자정보

#### 석동열 박사과정 대학원생

● 소속 : 한국과학기술원

● 연구분야 : 바이오메디컬 응용 회로설계(센서 및 신호처리)

• 이메일 : sukd10@kaist.ac.kr

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 30 Continuous-Time ADCs**

이번 2025 IEEE CICC의 Session 30은 Continuous-Time ADCs라는 주제로 총 4편의 논문이 발표되었다. 3편의 논문은 높은 해상도를 얻기 위해 noise-shaping을 적용한 CT DSM 구조의 논문이었으며, 1개의 논문은 넓은 대역폭을 얻기 위한 CT pipeline ADC를 제안하였다. 본 review에서는 그 중 30-2, 30-3, 30-4를 리뷰하고자 한다.

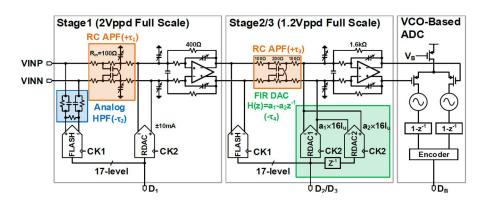

#30-2 본 논문은 Tsinghua university에서 발표한 연구로, CT pipeline ADC에서 signal path 와 quantization path간 발생하는 delay mismatch 문제를 해결하기 위해 각 stage 별로서로 다른 delay alignment technique을 활용한 hybrid 구조를 제안하였다. CT pipeline ADC에서는 quantization하고, DAC이 동작하기 까지의 delay가 signal에 leakage가 발생하게 된다. 기존에는 LC lattice 구조를 사용하거나 RC all-pass filter (APF)를 사용하였지만, 면적이 너무 크거나 delay alignment가 부정확하였다. Time-interleaving 구조도 제안되었으나 전력소모와 면적이 매우 크게 증가한다는 단점을 가지고 있었다.

제안하는 구조에서 1<sup>st</sup> stage에는 RC APF에 더해 quantization path에 high-pass filter를 추가하여 analog negative delay를 형성함으로써, 필요한 RC APF의 delay 요구사항을 줄일 수 있었다. 2<sup>nd</sup> stage에서는 passive 소자들의 PVT variation을 개선하기 위하여 quantization path에 FIR DAC을 사용하였다. 결과적으로 제안된 hybrid delay alignment 구조를 통해, 73.8dB DR, 450MHz 대역폭, 0.16mm²을 달성하여 우수한 성능을 달성하였으며, PVT variation에 강인하면서도 area-efficient한 delay alignment 방식을 통해 163.2dB의 Schreier FoM을 달성하였다.

[그림 1] 제안하는 CT Pipeline ADC 구조

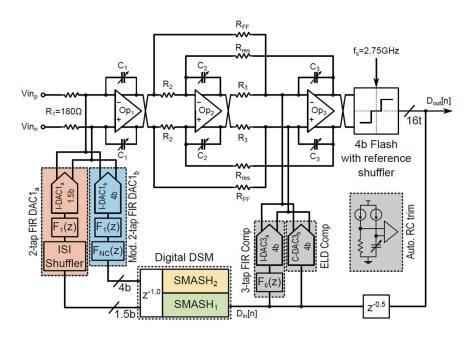

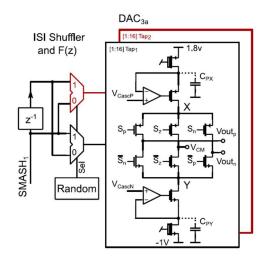

#30-3 본 논문은 University of Ulm에서 발표한 연구로, CT DSM에서 multi-bit quantizer 를 사용하였을 때 DAC 간의 mismatch로 인해 발생하는 문제를 dual quantization 기반 sturdy MASH (SMASH) 구조와 inter-symbol interference (ISI) shuffler를 결합한 구조를 제 안하였다. Multi-bit CT DSM은 일반적으로 높은 해상도와 jitter robustness를 가지지만, DAC mismatch로 인해 linearity가 나빠지게 되고, 제안된 구조에서는 2-2 SMASH 구조의 digital DSM (DDSM)를 사용하여 DAC을 2개로 분리하여 구현하였다. DAC1a는 signal path 를 담당하며, 해당 DAC에 해당하는 1.5b quantization noise는 DAC1b에 의해 noise-coupling 되어 고해상도를 도달함과 동시에 linearity requirement를 크게 줄일 수 있었다.

[그림 2] 제안하는 Dual quantization CT DSM 구조

또한, ISI의 영향을 줄이기 위해 FIR DAC인 DAC1a tap 수를 random하게 shuffling하여 logic의 rise time과 fall time을 랜덤화 하였고, headroom과 noise 성능을 위하여 supply voltage를 사용하였다. 또한, reference folding과 zipper reference shuffling [1] 기법을 4b flash quantizer에 추가하여 동작 속도를 향상시킴과 동시에 전력 효율을 높일 수 있었다. 결과적으로 제안된 구조는 2.75GHz의 높은 동작 주파수에, 80MHz 대역폭 및 71dB의 SNDR을 43.3mW의 전력만을 소모하면서 달성하여, 163.7dB의 Schreier FoM을 달성하였다. 또한, mismatch tone들을 shuffling을 통해 제거하여 calibration없이 106.2dB의 높은 SFDR을 달성할 수 있었다.

[그림 3] 제안하는 ISI Shuffler 구조

#30-4 본 논문은 Tsinghua university에서 발표한 연구로, 1-bit CT DSM의 feedback DAC으로 인한 OTA의 높은 전력 소모 및 jitter sensitivity문제를 해결하기 위해 direct charge dump (DCD) technique을 제안하였다. 기존 1-bit CT DSM은 calibration-free하고, loop filter의 loading이 작다는 장점을 가지고 있지만, 첫번째 integrator의 OTA가 1-bit DAC을 빠르게 따라가야 해 전력 소모가 매우 크며, sampling jitter에 민감한 특징을 가지고 있어, Schreier FoM이 multi-bit에 비해 부족하다.

[그림 4] 제안하는 DCD기술이 적용된 CT DSM 구조

제안하는 DCD 구조는 기존 방식과 다르게 OTA가 feedback 경로에 관여하지 않고, feedback capacitor에 저장된 charge를 integration capacitor에 dump하여 integration을 진행하게 된다. 이를 통해 OTA는 input signal에 대해서만 처리하기 때문에 OTA1의 전력 소모를 1.5mW까지 줄일 수 있었다. 또한, 기존 NRZ current DAC을 활용한 구조보다 높

은 jitter tolerance를 달성할 수 있었으며, CT DSM의 anti-aliasing 특성을 유지하기 위해서 ping-pong operation을 적용하여 loop filter의 특성을 유지하고자 하였다. 프로토타입은 4차 noise-shaping을 달성하였으며 3.2GS/s에서 76.3/73.2dB의 SNDR을 25/40MHz 대역폭에서 얻어내었고, 4.2mW만을 사용하여 174.0/172.9dB의 Schreier FoM을 달성하였다.

### 참고문헌

[1] T. Caldwell *et al.*, "A Reconfigurable  $\Delta\Sigma$  ADC With Up to 100 MHz Bandwidth Using Flash Reference Shuffling," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 8, pp. 2263-2271, Aug. 2014.

## 저자정보

### 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야: Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

• 홈페이지 : https://impact.kaist.ac.kr

단국대학교 파운드리공학과 석사과정 조혁준

## Session 35 High-Resolution and Noise-Shaping ADCs

Session 35에서는 고해상도 응용 분야에 적합한 고성능 ADC를 주제로 총 8편의 논문이 발표되었다. 최근에는 CT  $\Delta$   $\Sigma$  ADC와 멀티 비트 양자화를 활용한 2단계 Zoom ADC 구조에 관한 연구가 진행되고 있으며, 이러한 구조에서는 DAC mismatch로 인한 선형성 저하가 주요한 과제로 부상하고 있다. 기존에는 이를 해결하기 위해 DEM(Data-Weighted Averaging)이나 MES(Mismatch Error Shaping) 기법이 사용되었으나, 이러한 방식은 낮은 OSR 환경에서 shaping 효과가 감소하고, 입력 주파수가 증가할수록 비선형성이 심화하며, 동시에 회로 복잡성과 전력 소모 증가라는 한계를 갖는다. 이번 세션에서는 이러한 문제를 해결하고자, FIR DAC를 도입하여 DEM이나 MES 없이도 고 선형성을 구현한 Zoom ADC, CT  $\Delta$   $\Sigma$  ADC, 그리고 Tri-level 구조와 보정 기법을 통해 선형성을 개선한 ADC 논문들이 발표되었으며, 본 리뷰에서는 이들 주요 연구를 중심으로 살펴보고자 한다.

#35-1 본 논문은 마카오대학교에서 발표한 논문으로, 고성능 ADC에서 발생하는 높은 OSR과 전원 전압 요구로 인한 전력 소모, 클럭 오버헤드, 전원/접지 잡음 및 면적 부담 문제를 지적한다. 이를 해결하기 위해, 낮은 OSR에서도 높은 SNDR과 에너지 효율을 달 성할 수 있는 CT-Zoom ADC 구조를 제안한다. 제안된 CT-Zoom ADC는 AA 필터, 5-bit SAR Coarse ADC, 3차 CRFF 루프 필터, 3-bit 2차 NS Fine ADC, 그리고 저항 기반 Tri-level DAC로 구성된다. Zoom 구조를 통해 루프 필터 입력 전 신호를 줄이고, 5차 Noise Shaping을 통해 낮은 OSR에서도 고성능을 유지한다. 하지만 기존 DEM 기반 DAC mismatch shaping은 낮은 OSR 및 고주파 입력에서 성능 저하가 심하다. 이를 해결하기 위해, 본 논문은 Reset Tri-level DWN(RST-TDWA)와 Foreground calibration을 도입한다. RST-TDWA는 포인터 동작의 주기성을 활용해 mismatch 오류를 1차 shaping 된 이진 신 호로 변형시켜 SNR 향상을 달성한다. 또한, Tri-level DAC 구조는 저항 수를 줄이고 안정 성 및 낮은 Flicker Noise를 확보하며, RF와 CF로 구성된 패시브 필터는 약 70dB의 앨리 어싱 억제를 제공한다. Coarse ADC는 패시브 전하 공유 방식으로 Fine ADC에 전달되며, RC 필터를 통해 사전 필터링되어 높은 앨리어싱 억제 성능을 유지한다. 제안된 ADC는 65nm CMOS 공정으로 제작되었으며, 105.4dB SNDR, 105.7dB SNR, 106.3dB DR를 달성하 였고, 최종적으로, 48x OSR 환경에서 186.0dB의 FoM<sub>SNDR</sub>을 기록하였다.

[그림 1] 제안된 CT-Zoom ADC의 회로도

#35-5 본 논문은 중국 베이징대학교에서 발표된 연구로, 고성능 CTDSM에서 멀티 비트양자화기는 해상도 향상에 유리하지만, DAC 불일치로 인해 DEM 회로의 복잡성과 전력소모가 증가하는 한계를 가진다. 반면, 싱글 비트 양자화기는 구조가 단순하고 선형성이우수하나, 큰 양자화 잡음과 적분기 선형성 확보의 어려움이 존재한다. 이를 해결하기 위해 본 논문에서는 Hybrid Gm-Boosting OTA와 Tri-Level FIR DAC를 결합한 CTDSM 구조를제안한다. 제안된 CTDSM은 2단 피드 포워드 구조의 Hybrid Gm-Boosting OTA를 도입하여 잡음과 대역폭을 독립적으로 최적화하며, 각 Gm 블록은 기능에 따라 분리 설계된다. Gm1은 저 잡음과 넓은 대역폭을, Gm2와 Gm3는 높은 DC 이득을 제공하고, GmF는 입력 부스트 OTA를 통해 높은 GBW와 넓은 출력 스윙을 확보하며 주파수 보상을 수행한다. 또한, 양자화기에는 Tri-Level FIR DAC을 적용하여 양자화 잡음을 저감하고 선형성을 향상했으며, FIR 필터에는 Chopping을 통해 Flicker Noise를 억제하고 앨리어싱을 방지한다. DAC는 저 잡음과 구현 용이성을 고려해 저항 기반으로 구성되었다. 제안된 CTDSM은 별도의 DEM이나 보정 회로 없이도 고성능을 구현하며, 180nm 공정에서 제작되어 20kHz 대역폭과 128의 OSR 환경에서 99.5dB의 SNDR, 104dB의 DR, 182.1dB의 FoM<sub>SNDR</sub>을 달성하였다.

[그림 1] 제안된 CTDSM의 구조와 1st 적분기의 OTA 회로도

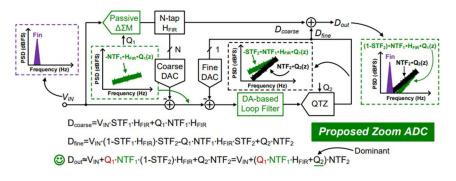

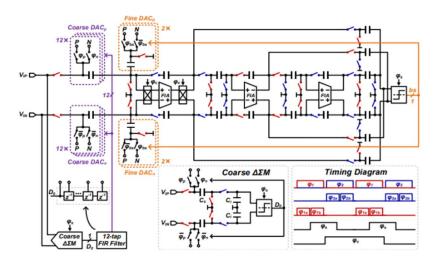

#35-6 본 논문은 중국 시안전자과기대학교에서 발표된 연구로, SAR과 델타-시그마 ADC를 결합한 Zoom ADC 구조에서 발생하는 양자화 잡음 누설과 DAC 선형성 문제를 해결하고자 한다. 이를 위해 Coarse 단계에 완전 패시브 1차 델타-시그마 모듈레이터를 도입하여 증폭기 없이도 Noise Shaping을 구현하고, FIR DAC를 활용해 DAC mismatch를 개선함으로써 고선형·고효율 스위치드 커패시터 Zoom ADC를 제안한다. 제안된 구조는 스테이지 간 양자화 잡음 누설을 억제하면서도 전력 소모를 낮추며, 12 탭 FIR 필터를 통해본질적으로 선형적인 멀티 비트 피드백 경로를 구현하여 DWA나 별도의 보정 없이도 높은 선형성을 확보하였다. Fine 단계는 FIA 기반 증폭기를 사용하는 델타-시그마 모듈레이터로 구성되어, 높은 이득 선형성과 정적 전류 소모 제거, 샘플링 속도에 따른 전력 조절특성을 갖는다. 제안된 ADC는 65nm 공정으로 제작되었으며, 5.12 MS/s 샘플링 속도에서 100.7 μ W를 소모하면서 101.1dB의 SNDR, 123.5dB의 SFDR, 121.2dB의 THD, 183.9dB의 FoMDR 성능을 달성하였다. 특히 별도 보정 없이 -120dB 이하의 THD를 통해 초고선형성을 달성하였다.

[그림 1] 제안된 Zoom ADC

[그림 2] 제안된 Zoom ADC의 상세 회로 및 타이밍 다이어그램

# 저자정보

## 조혁준 석사과정 대학원생

● 소속 : 단국대학교 파운드리공학부

● 연구분야: Biomedical Circuits ● 이메일: sdi5236@dankook.ac.kr

● 홈페이지: https://sites.google.com/dankook.ac.kr/acs-lab